JUUU

# The National Semiconductor Economic Roadmap

Sp

DECEMBER 2022

The National Semiconductor Economic Roadmap was conceived and commissioned by the Arizona Commerce Authority (ACA) and developed by industry leaders, academic institutions, state entities, and Boston Consulting Group

n today's tech-based world, semiconductors are critical components for a wide range of products across every industry. Despite a global, connected economy, the pandemic disruptions of 2020 exposed the need to enhance resiliency across the entire semiconductor value chain. To ensure national security and economic stability, the US recognized the need to focus on competitiveness in every aspect of the semiconductor industry.

Arizona has long been a top state for semiconductor industry investments and growth. As our own experience demonstrates, states are on the front lines of semiconductor innovation. It was with this in mind that, under Arizona Governor Doug Ducey's leadership, the Arizona Commerce Authority set out to convene a diverse coalition and create the National Semiconductor Economic Roadmap (NSER).

This first-of-its-kind roadmap is an industry-led initiative designed to advance semiconductor competitiveness and craft a blueprint to future-proof semiconductor manufacturing in the US. More than 80 industry leaders, educational institutions and public sector leaders from states around the nation came together to collaborate and develop the NSER, which outlines goals and objectives across four key pillars: infrastructure, supply chain, workforce, and entrepreneurship.

With the CHIPS Act now passed by Congress and signed into law by the President, the NSER is more critical than ever and will help to guide initiatives to advance cutting-edge semiconductor research, development, design and manufacturing.

We are very grateful for the time and expertise our many partners have contributed to creating this robust, actionable plan. It has been an honor to convene this historic effort and develop a shared vision, one that will drive US leadership in the semiconductor industry for decades to come.

Sandra Watson President & CEO Arizona Commerce Authority

# **Table of Contents**

| Executive Summary                                           | 6  |

|-------------------------------------------------------------|----|

| Introduction to the National Semiconductor Economic Roadmap | 9  |

| Semiconductor Value Chain                                   | 10 |

| NSER Domains                                                | 12 |

| NSER Scenario                                               | 13 |

| Chapter 1: Infrastructure                                   | 15 |

| Context                                                     | 15 |

| NSER Action Plan                                            | 18 |

| Chapter 2: Supply Chain                                     | 21 |

| Context                                                     | 21 |

| NSER Action Plan                                            | 23 |

| Chapter 3: Workforce                                        | 26 |

| Context                                                     | 26 |

| NSER Action Plan                                            | 30 |

| Chapter 4: Entrepreneurship                                 | 37 |

| Context                                                     | 37 |

| NSER Action Plan                                            | 39 |

| Conclusion                                                  | 42 |

# **Executive Summary**

The recent global semiconductor shortage has spotlighted the need to boost the resilience of the entire semiconductor ecosystem. The constrained supply and booming demand of 2020–2022 underscored the disruption that a deficit of semiconductors can cause across the global economy. Even beyond the economic impact, the effects of potential shortages in semiconductors for aerospace, defense, energy, and other essential arenas of infrastructure are of particular concern.

The semiconductor industry has come to rely on a complex global ecosystem to thrive. The US has long been a significant contributor; however, manufacturing capacity has shifted over the past 30 years and the US ecosystem has weakened relative to other regions.

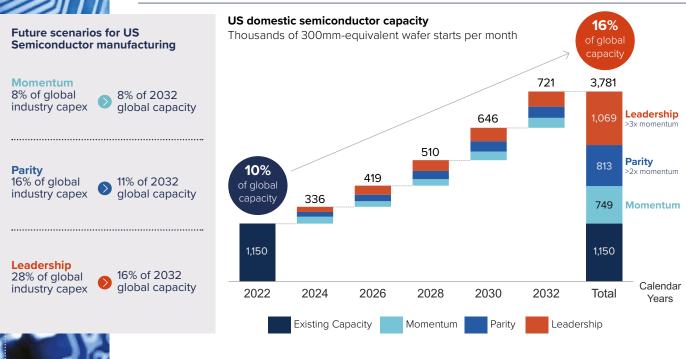

Based on recent patterns of global investment, the US would have captured an estimated 8% of global capital expenditure from 2023 to 2033 and seen its overall share of global semiconductor manufacturing capacity decline from approximately 10% in 2022 to 8% by 2033.

However, in a significant bipartisan step, the CHIPS and Science Act was signed into law in August 2022, appropriating \$52 billion and creating a five-year investment tax credit to support expanding the US semiconductor industry. To realize the full value of the CHIPS Act and meaningfully strengthen both US competitiveness and global resilience for decades to come, policy makers, industry players, academia, and other stakeholders must work together to improve and support the entire manufacturing ecosystem, broadly grouped into the domains of infrastructure, supply chain, workforce, and entrepreneurship.

Released December 2022, the National Semiconductor Economic Roadmap (NSER, pronounced "answer") establishes a baseline and a target state for the four domains using rigorous data and analyses. The NSER industryled action plan to achieve these targets serves as a single source of truth for all semiconductor industry players as well as other private and public stakeholders.

If the path laid out in NSER is followed, the US could reasonably capture two to four times more investment than it otherwise would have—16% to 28% of global industry capital rather than 8%— and anticipate its share of all global capacity to be 50% to 200% higher, translating to 11% to 16% of total global capacity in 2032 instead of 8%.

### INFRASTRUCTURE

Infrastructure is perhaps the most critical domain. As defined in NSER, it includes wafer fabrication capacity; infrastructure for training and R&D; and supporting infrastructure such as water, energy, and waste utilities.

NSER has identified three visions for the infrastructure domain:

- Align the domestic regulatory and incentive environment with competing global capital destinations to increase the financial attractiveness of the US.

- Invest in and create a suitable environment for R&D within the US to encourage collaboration and cooperation.

- Transition and modernize the utility infrastructure to increase resiliency and water reclamation and reduce manufacturing-related carbon emissions with the end goal of reaching net zero.

# **SUPPLY CHAIN**

Semiconductor manufacturers rely on access to a global supply chain of materials, equipment, and package, assembly, and test capacity, as well as open access to end markets. NSER has identified three visions for the supply chain domain:

- Establish dependable supply chains and support multiple qualified vendors for raw materials, consumables, intermediary products, and equipment to sustain domestic manufacturing.

- Increase domestic manufacturing capacity for advanced and mature semiconductor devices.

- Maintain US access to global markets and improve visibility into the supply chain to promote innovation.

# WORKFORCE

The industry's ability to meet the demand for talent is a persistent concern among industry leaders—not surprising, given the global shortage of construction workers, technicians, operators, scientists, and engineers. Without the necessary workforce, sustainable competitiveness in the industry will be impossible.

To overcome these challenges, NSER has identified the following visions for the workforce domain:

- Increase the number and diversity of students who pursue education in the semiconductorrelated fields and support their transition into the industry.

- Retain skilled workers in the semiconductor industry by addressing select causes of attrition, such as improving DEI efforts and creating clear development paths.

- Ensure that the workforce has the competencies required to support the continued advancement and needs of the industry.

# **ENTREPRENEURSHIP**

Entrepreneurship—both across the value chain and in supporting industries—is crucial to ongoing innovation and competitiveness. However, startups face tremendous challenges in this space, including a lack of investment, access to research facilities, and cross-sector collaboration. To overcome these challenges, NSER has identified the following visions for the entrepreneurship domain:

- Increase private equity, government, academic, and company investment in semiconductor entrepreneurs.

- Increase access to government, academic, and private facilities and resources needed to conduct critical R&D.

- Generate a spirit of collaboration between research universities, startups, and industry players and create bridges of collaboration between these groups that are focused on semiconductor innovation.

The current semiconductor shortage has prompted not only the US but many other countries to adopt measures to boost resiliency and safeguard their own national and economic security through greater innovation, reshoring, and trade controls.

With the passage of the CHIPS Act, the US has a generational opportunity to increase its competitiveness and global market share across the semiconductor value chain in a way that also improves global resilience.

If it is to capture this opportunity, the US must act today, pursuing a course of rapid and disciplined execution of the key visions laid out in NSER and endorsed by leaders across the industry, academia, and public sector.

NSER was conceived and commissioned by the Arizona Commerce Authority (ACA) and developed by industry leaders, academic institutions, public entities, and Boston Consulting Group.

Read the full report for more information about the challenges facing the semiconductor industry and the steps the US must take to become a competitive destination for semiconductor value chain activities long term.

For any inquiries or to become part of future NSER work, please email NSER@AZcommerce.com.

# Introduction to the National Semiconductor Economic Roadmap

The National Semiconductor Economic Roadmap (NSER) is a ten-year, industry-led action plan to increase US competitiveness in the semiconductor industry and strengthen semiconductor supply chain resiliency. Leaders in industry, academia, and the public sector developed NSER to align industry, motivate stakeholders, and support the creation of optimal public policy moves. In addition, NSER is intended to offer a trusted source of rigorous data and analyses to all participants and stakeholders interested in furthering the industry, as well as delineate the US industry's broad requirements for increasing its global competitiveness.

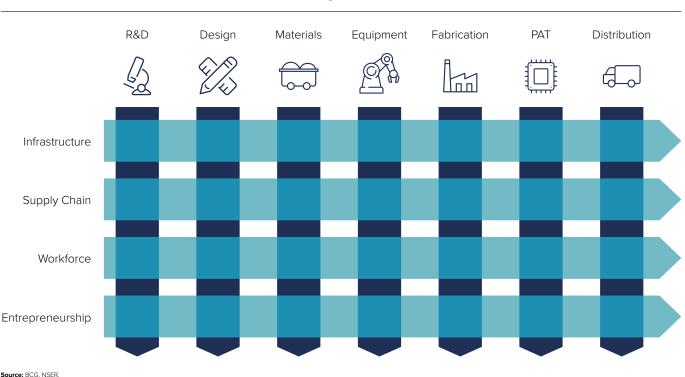

NSER charts a path through which the US can increase its global competitiveness across the entire value chain by acting across four domains: infrastructure, supply chain, workforce, and entrepreneurship.

Now that Congress has appropriated funds for the CHIPS Act, the US has the potential to be a more competitive region for business expansion in the near term if execution is speedy and meets stated goals. The bill includes \$39 billion in incentives for semiconductor manufacturing, \$11 billion in incentives for semiconductor R&D, and a 25% investment tax credit for qualified investments in advanced manufacturing facilities between January 1, 2023, and January 1, 2027. During this period, the US is primed to capture a substantial share of new semiconductor investments.

As a result, the US is likely to see a two-tothree-fold increase in semiconductor-related investments in the US over the next ten years. However, CHIPS is only the beginning, and without a concerted focus on increasing domestic competitiveness, the US will lose any edge afforded by CHIPS once the funds are depleted and the investment tax credit ends.

It was this need for sustained competitiveness that motivated NSER. Through the action plans laid out in NSER, the US can remain competitive over the longer term, building on the benefits created by CHIPS.

#### Exhibit 1. NSER Addresses Four Domains Affecting the Semiconductor Value Chain

Note: PAT = package, assembly, and test.

# **Semiconductor Value Chain**

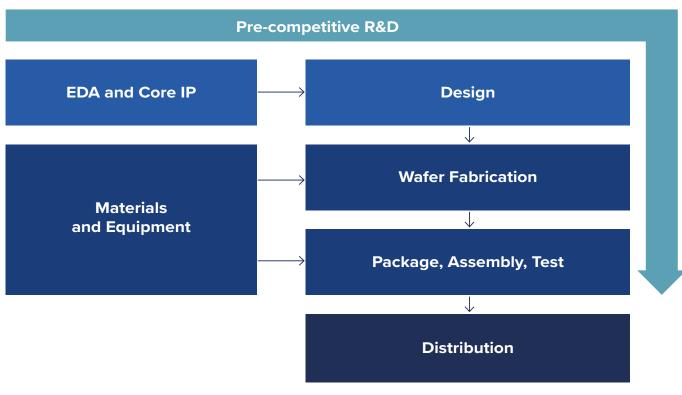

Semiconductors are produced within a complex global value chain consisting of four key steps: R&D; design; semiconductor manufacturing, broken into wafer fabrication and package, assembly, and test (PAT); and distribution. Design requires electronic design automation (EDA) and core intellectual property (IP), while manufacturing requires materials and equipment.

# **Pre-competitive R&D**

R&D is essential to the ever-evolving tools, techniques, processes, and final devices supporting and produced by the semiconductor value chain. Funding for and execution of R&D is driven by private enterprises, universities, governments, and nonprofits.

# Design

Semiconductor design includes the use of various software packages for algorithm development, architecture building, and integrated circuit design as well as for designing the physical layout of semiconductor products and verifying their functionality.

# **Design: EDA and Core IP**

Design requires EDA and core IP building blocks. EDA tools enable designers to create a digital layout of a semiconductor to simulate its functionality with billions of interacting transistors and other components. Given the growing complexity of semiconductors, designers will often use existing IP building blocks to speed up the process rather than re-designing every chip from scratch.

#### Exhibit 2. The Semiconductor Value Chain Flow

Source: BCG. Note: EDA = Electronic design automation.

# **Wafer Fabrication**

Wafer fabrication, sometimes referred to as front-end manufacturing, is a highly technical and involved process with 5 key steps being repeated hundreds of times. The process starts with a blank silicon wafer which undergoes oxidation and coating, lithography, etching, doping, and metal deposition and etching. The final wafer will contain up to hundreds of identical integrated circuits ready for PAT.

# Package, Assembly, and Test

PAT, also known as back-end manufacturing, is the process of preparing devices for their ultimate application. Whole wafers are tested for basic functionality before being diced into individual devices, mounted on lead frame or package substrate, electrically connected and bonded to output pads, and given a hard, protective external shell. PAT may be performed in-house at an IDM or by an outsourced assembly and test (OSAT) facility.

# **Manufacturing: Materials**

Wafer fabrication and package, assembly, and test processes require hundreds of different raw, processed, and manufactured materials, including wet chemicals, gases, metals, silicon wafers, and packaging.

# **Manufacturing: Equipment**

Each step of wafer fabrication and PAT requires specialized equipment for handling, processing, cleaning, and testing wafers and individual chips. Equipment systems include critical subsystems and critical components. These systems are extremely costly and in some cases are only manufactured by a few companies due to the sophistication of the machinery.

# Distribution

Distributors serve as intermediaries between semiconductor manufacturers and end users or original equipment manufacturers (OEMs) who install the semiconductors into devices such as computers, electronics, and cars. While semiconductor manufacturers typically distribute directly to large OEMs, they often leverage external distributors for smaller OEMs. Distributors can provide sales support, technical support, local expertise, and logistics coordination.

# **NSER Domains**

NSER is organized into four domains that NSER participants have identified as critical to US semiconductor industry competitiveness.

# INFRASTRUCTURE

**NSER Scope:** The infrastructure domain includes initiatives that result in more resilient and robust physical assets, such as R&D and training and education facilities, manufacturing facilities, utilities, transportation, and shovel-ready sites with advanced or expedited permitting.

**Challenges:** Building and maintaining the infrastructure to support the industry requires substantial, long-term capital commitments, and nations in East Asia have been investing public funds for decades to help shoulder the cost.

### **SUPPLY CHAIN**

**NSER Scope:** The supply chain domain includes initiatives that increase the resilience of the global movement of chemicals and materials, equipment, EDA, core IP, and semiconductor manufacturing products as well as supply chain management and distribution.

**Challenges:** Steps in the supply chain tend to be concentrated in a few geographic regions. This concentration increases the threat of disruption from a variety of causes, including those from natural disasters or geopolitical conflict. The risk of disruption is difficult to predict or mitigate due to a lack of visibility into the supply of upstream raw materials and other inputs. Further, this concentration of the supply chain is reinforced by existing ecosystems and regional comparative advantages.

#### WORKFORCE

**NSER Scope:** The workforce domain includes initiatives that build a strong pipeline of management, engineers, scientists, operators, and technicians. It also encompasses the skilled tradespeople, such as construction workers, electricians, and welders, who build the facilities used across the value chain.

**Challenges:** Access to talent is commonly cited as the top issue facing semiconductor players across the value chain. Companies experience increasing competition from other industries, other countries, and other companies within the industry and are increasingly challenged to find and retain the talent they require.

# **ENTREPRENEURSHIP**

**NSER Scope:** The entrepreneurship domain includes initiatives that will result in new businesses that build breakthrough technology and develop IP or other proprietary advantages at any stage of the semiconductor value chain.

**Challenges:** Entrepreneurial semiconductor ventures have significant barriers to market entry because the industry is incredibly R&D and capital intensive. Innovations in this space often require years of R&D, deep expertise, and the ability to use existing IP. Further, access to facilities, materials, and equipment to prototype startup products is limited and expensive.

# **NSER Scenario**

The semiconductor value chain is at an inflection point today. Regional bottlenecks, geopolitical tensions, mismatches between supply and demand, and policy decisions by different governments are poised to trigger a dramatic remaking of the industry.

Depending on its level of competitiveness, the US will attract some share of the estimated \$2 trillion to be invested in semiconductor wafer fabrication over the next 10 years.

#### Momentum

The US has been economically unattractive relative to other semiconductor manufacturing regions such as Taiwan, South Korea, and mainland China for at least three decades. This has resulted in declining capital investments in the US and therefore declining share of global capacity. If the trajectory of the past five years were to continue through 2032, the US would be poised to capture only 8% of global capital investments in manufacturing, and the US share of global wafer fabrication capacity would fall to 8% from around 10% today.

# Parity

The CHIPS Act, if deployed quickly and effectively as urged in NSER, will enhance US competitiveness creating parity with other comparable markets (e.g., Taiwan and South Korea) while funds last and the ITC is in effect. By following the path laid out in NSER to improve all domains, the US may maintain this competitiveness for the next 10 years and could capture 16%<sup>1</sup> of global industry capital investment through 2032 (Twice the momentum case) by increasing the share of non-US-company foreign direct

#### Exhibit 3. US Semiconductor Economic Roadmap: Future Capital Investment Scenarios

#### Source: Semiconductor company financials; BCG analysis.

Note: In Momentum, the US continues its 2017–2022 investment trajectory through 2032. In Parity, the US is more competitive than historically and therefore attracts 75% of US company capital investments and an incremental 50% of non-US company foreign direct investment (FDI) bound for countries outside the US. In Leadership, the US becomes not just competitive but attractive, and therefore attracts 75% of US company capital investments and 25% of all capex (not just FDI) of non-US companies (excluding mainland China).

Assuming the US attracts 25% of investments by non-US companies that would otherwise be made outside of their home countries as well as 75% of investments by US companies. investments it receives and the share of US company capital invested domestically. In this scenario, the US share of global capacity would increase to 11%, approximately 38% increase relative to Momentum.

#### Leadership

If rather than achieving parity, the US can become the most competitive country for semiconductor companies to do business by following NSER to make the US equal to or better than comparable regions in all domains. In this scenario, would be possible for the US to capture 28%<sup>2</sup> of global industry capital investments and grow its share of global capacity to 16% by 2032, approximately 100% increase relative to Momentum. Aside from being an important overall indicator of competitiveness, understanding these scenarios is foundational to NSER as wafer fabrication is a major driver of the broader semiconductor ecosystem.

The following chapters of NSER are organized by domain to articulate what the industry will require to achieve the Leadership Scenario.

#### Exhibit 4. Four Domains Critical to Achieving Growth in Semiconductor Fabrication

#### Infrastructure

- Fabs themselves are a form of infrastructure that offers space for R&D, training, and education.

- Fabs require substantial infrastructure to operate, including water, energy, and transportation.

#### Supply Chain

- Wafer fabrication requires thousands of inputs, and suppliers will often locate their operations nearby.

- Final products must also be distributed to customers across the world as components of other products.

#### Source: BCG analysis

2. Assuming the US attracts 25% of investments by non-US companies as well as 75% of investments by US companies.

# CONTEXT

Infrastructure underpins the ability of every other semiconductor domain to advance. The supply chain requires manufacturing sites, equipment, and transportation; the workforce must have facilities to educate and train future talent; entrepreneurship requires R&D facilities; and all need physical and digital infrastructure to share and store knowledge. But this infrastructure is extremely expensive to build and maintain.

In aggregate, the semiconductor industry has a ratio of capital expenditure to revenues of more than 20%, making it one of the most capital-intensive sectors in the US economy, alongside utilities.<sup>3</sup>

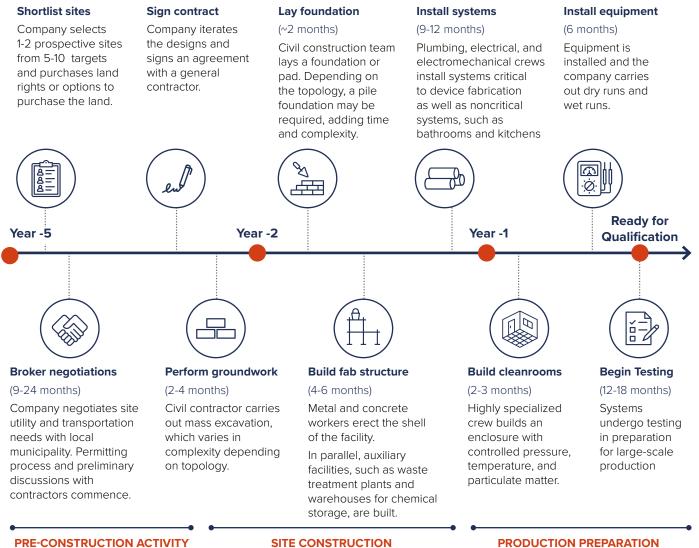

### Exhibit 5. Fabs Require Five Years or More of Planning and Construction

Semiconductor firm, general contractor, and government

Source: BCG, NSER.

General contractor. civil engineering firms

General contractor, highly specialized crews

3. BCG/SIA, "Strengthening the Global Semiconductor Value Chain in an Uncertain Era," April 2021.

Further, deployment of the required capital, and development of the required infrastructure, is time-consuming and complex. The illustrative, high-level example of building a large semiconductor fabrication facility shown below provides a sense of its complexity. Constructing a fab can be a more than five-year process of site selection, permitting, construction, and ramp up.

Semiconductor activities require hundreds, if not thousands, of acres of land with proper permits to build and operate. The process of shortlisting a site for a fab and then acquiring land rights and permits—all before breaking ground—takes years of planning and negotiation. Afterward, constructing the fab can take more than two years. In the US, the full cost of constructing and equipping an advanced logic fab can exceed \$20 billion, and even a less costly analog fab can exceed \$5 billion. Much of this cost comes from the equipment, so building smaller physical facilities for training or R&D does not proportionally scale down the cost.

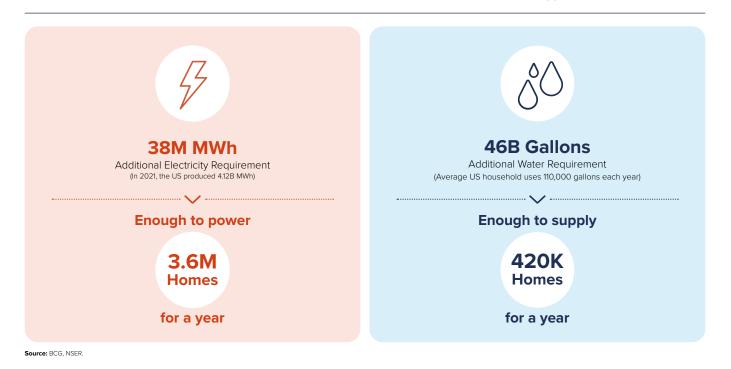

The selected site must have access to sufficient wet and dry utilities. Frequently, the project must expand these utilities, which further adds to the already high cost of construction. While water consumption has been declining due to the industry's strong efforts to innovate in the manufacturing process and increase reclamation, water is heavily utilized during semiconductor manufacturing processes to clean and cool equipment as well as produce electricity. In the Leadership Scenario, the additional production will use 50 billion gallons of water a year, and local infrastructure will need to be augmented to meet intake demands and handle the resulting wastewater processing.

A stable supply of electricity is also necessary, which is not always a given in the US. To achieve the Leadership Scenario, roughly 38 million MWh of electricity will be required to accommodate wafer production. If this energy is generated through new renewables production, it will require an over \$20 billion investment into wind and solar farms along with additional investment into grid expansion. Government policymakers will need to plan for the unique water and energy infrastructure requirements of the semiconductor industry to support major new manufacturing facilities but will also reap second-order benefits from increased sustainability of their infrastructure base.

#### Exhibit 6. The Leadership Scenario Requires Substantial Water and Energy Infrastructure

In addition to increasing utility capacity, states must prioritize improving the resiliency of existing, aging physical infrastructure through measures such as weatherproofing power grids and ensuring stable access to water during extreme weather. These improvements will ensure that fabs can manufacture year-round without disruptions, and are made more critical, as the country is likely to face increased pressure on water and energy in the future due to climate instability and rising demands on existing infrastructure. In Texas, for example, the annual cost of winterizing the energy grid and preventing disruptions is an estimated \$85 million to \$200 million.<sup>4</sup>

Finally, access to training centers and high-tech labs is necessary to acquire the talent and knowhow for semiconductor activities, and these are often housed at institutions of higher education. Companies therefore often strategically build near research universities. Expanding the capacity and reach of educational and R&D facilities would aid in training, reskilling, and upskilling the existing and future workforce as well as provide more opportunities for innovation. Fostering cooperation across the industry through collaboration infrastructure, such as data-sharing tools and protocols, could expand knowledge sharing while still protecting IP.

Given the extent of the infrastructure needed to support the semiconductor industry, the importance of strengthening this domain is no surprise, particularly if growth is to occur. To succeed, US infrastructure must become more cost competitive. At present, the US has a ten-year TCO that is 30% higher than that of comparable East Asian economies, where government incentives have highly subsidized semiconductor manufacturing costs, and labor and land costs are lower.<sup>5</sup> Further, construction time in the US exceeds that of South Korea by 20% or more, delaying the payback period.<sup>6</sup> The estimated decline in US market share for modern semiconductor wafer capacityfrom 37% in 1990 to 12% in 2020—was in large part due to the difference in TCO that these elements have generated.7

The US must catch up to decades of investment abroad as well as face increased headwinds from renewed foreign investments. Mainland China, South Korea, and several EU member states have announced initiatives to invest billions of dollars to expand their own infrastructure.

The following plan lays out the actions necessary to build resilient and robust infrastructure for US semiconductor industry growth. Improvements to physical infrastructure resources supported by local, state, and federal governments, coupled with expedited permitting and competitive incentives, will lead to expanded activity and innovation along the value chain long term.

- 4. Federal Reserve Bank of Dallas, "Cost of Texas' 2021 Deep Freeze Justifies Weatherization," April 2021.

- 5. BCG/SIA, "Government Incentives and US Competitiveness in Semiconductor Manufacturing," September 2020.

- 6. CSET, "No Permits, No Fabs," October 2021.

- 7. BCG/SIA, "Government Incentives and US Competitiveness in Semiconductor Manufacturing," September 2020.

Based on an extensive literature review and input from industry, government, and academic leaders, NSER participants have identified three visions for improving domestic semiconductor infrastructure. Intended to generate long-term change, these visions evolve through a series of near-term initiatives and are therefore responsive to new developments within the semiconductor industry as they occur.

#### **VISION:**

US regulations and incentives programs make the US the world's most attractive destination for building semiconductor industry infrastructure.

**Objective:** Improve state and local infrastructure and use national incentives to attract semiconductor manufacturing activities.

- **Initiative:** Rapidly allocate and disburse funding for infrastructure improvements and explore all means to reach and maintain cost parity.

- **Initiative:** Support companies in meeting the requirements for receiving federal incentives.

- Initiative: Encourage US Department of Commerce (DOC) to collaborate with industry, academic, and government officials to quickly disburse CHIPS funding to the areas of greatest need and impact.

- Initiative: To ensure sustained growth in R&D and manufacturing, government to assess the value of to extending CHIPS Act incentives, including the investment tax credit.

**Objective:** Increase the number of pre-permitted and zoned shovel- ready sites to accommodate manufacturing expansion.

- **Initiative:** Create an expedited EPA review for semiconductor manufacturing activities to decrease the time required for pre-construction activities.

- **Initiative:** Identify infrastructure gaps at prospective sites and coordinate with federal, state, and local government to ensure that those needs can be met.

- **Initiative:** Build local strategies to understand and plan for land-use and zoning requirements that could attract fabs and related projects.

#### **VISION:**

US infrastructure investment creates a strong environment for R&D, supporting world-leading collaboration on pre-competitive R&D.

**Objective:** Increase the capacity of educational, training, and research facilities needed to innovate and train workers.

$(\bigcirc)$

• Initiative: Rapidly deploy CHIPS funding to upgrade and expand public and private R&D facilities.

**Example:** The CHIPS Act allocates \$11 billion for DOC R&D activities at the National Semiconductor Technology Center, the National Advanced Packaging Manufacturing Program, the Manufacturing USA Semiconductor Institute, and Metrology R&D.

• **Initiative:** Develop in-person and virtual manufacturing-process training facilities (e.g., operating equipment, handling materials) to train workers across the semiconductor value chain, from doctoral students to operators.

**Example:** Through its Core Research Facilities, Arizona State University provides researchers and partners with access to state-of-the-art equipment, services, and training to help solve research challenges. Users include ASU faculty, students and staff, industry, small businesses/startups, other universities, research institutions, government agencies, and nonprofits.<sup>8</sup>

• **Initiative:** Leverage CHIPS resources to fund collaborative research programs at existing and new facilities.

**Objective:** Make use of collaboration tools and processes to facilitate knowledge and secure data sharing.

- **Initiative:** Use CHIPS resources to improve and deepen programs that collect and standardize reporting metrics for industry capital and R&D investment.

- **Initiative:** Use CHIPS funding to digitize and standardize the collection of emissions metrics for tracking progress across sustainability initiatives.

- **Initiative:** Publicize collaboration to create awareness of opportunities for working together, to generate excitement, and to increase the visibility of the industry.

**Example:** Northern Arizona University's cybersecurity program is a multidisciplinary and multistakeholder. Approximately \$10 million in research funds were secured from NAU, the Arizona Board of Regents, the National Science Foundation, the US Air Force, the Navy, and industry. About 24 students are involved in the cybersecurity team, including 16 PhD students. In the last four years, the team published 39 papers and 49 invention disclosures.<sup>9</sup>

$(\bigcirc)$

#### **VISION:**

US utility infrastructure is modern, resilient against disruptions, and sustainable long-term.

**Objective:** Modernize energy grids to secure reliable access to power from sustainable sources and protect operations from weather-related disruptions.

- **Initiative:** Weatherize the energy grids to protect them from extreme weather events, including heat and cold.

- Initiative: Modernize the energy grids, create redundancies in power transmission, and build storage for surplus energy.

- Initiative: Diversify power sources by encouraging the adoption of renewable energy sources.

**Example:** Samsung Austin Semiconductor fab, together with Apple and eBay, purchased 75 megawatts of power from a large-scale wind farm.<sup>10</sup>

- 8. ASU, "MacroTechnology Works a hub for semiconductors," 2022.

- 9. Sarah Melott, "AFRL partners with Northern Arizona University, DOD labs, industry to develop nanotechnology solutions to cyberattacks and cyber warfare," March 2020.

- 10. Samsung, "Apple, eBay, Samsung Austin Semiconductor and Sprint Accelerate Renewable Energy Development, November 2019.

Objective: Increase on-site water reclamation efforts, reduce the impact on watershed areas, and work towards net-zero water use.

• Initiative: Build and expand on- and off-site water recycling facilities with public-private partnerships.

**Example:** As part of ongoing water conservation efforts, TSMC recycled and reclaimed about 1.5 million metric tons of water from cooling towers, machines, and facilities in 2019.<sup>11</sup>

• Initiative: Update facilities and innovate in manufacturing processes to reduce water consumption.

**Example:** Intel implemented a process that optimizes or eliminates bypass flows. The company estimates that implementing projects like these at other fabs will lead to 625 million gallons of water saved annually by 2025.<sup>12</sup>

• Initiative: Diversify water sources in manufacturing facilities and create redundancies in the water supply to mitigate shortages.

Example: In addition to city water, TSMC has water reclamation plants in Yongkang and Anping, Tainan that supply the fabs with water.

Objective: Advance toward net-zero emissions in manufacturing by improving processes and incorporating alternative inputs.

• Initiative: Conduct an analysis of the carbon footprint of the semiconductor industry in the US and initiatives for reducing carbon emissions.

**Example:** SEMI recently announced the Semiconductor Climate Consortium to "drive progressive climate action within our industry value chain," which includes transparency and the reporting of Scope 1, 2, and 3 greenhouse gas emissions.<sup>13</sup>

• Initiative: Research and begin to incorporate replacements for environmentally harmful chemicals and gases.

**Example:** In the span of four years, the World Semiconductor Council voluntarily phased out perfluoro octane sulfonates (PFOS) emissions to near-zero levels.<sup>14</sup>

• Initiative: Increase the efficiency of manufacturing facilities so that production requires less energy and fewer harmful chemicals and gases.

**Example:** Intel is designing new fabs to meet Leadership in Energy and Environmental Design (LEED) standards and is investing in increasing the efficiency of existing fabs as part of a broader climate change commitment.15

**Example:** Since 2019, TSMC has reduced nitrous oxide by using high-temperature thermal wet scrubbers. The scrubbers reduced nitrous oxide by 90% and fluorinated greenhouse gases and ammonia by 99%.

• Initiative: Develop and deploy carbon capture technologies and destruction technologies for ozonedepleting substances to order to reduce emissions.

Example: Samsung's Carbon Capture Research Institute was established in 2021 to develop new carbon capture technologies and commercialize them for others to use. Achievements will first be applied to semiconductor production lines after 2030 and then to other parts of the company as well as its suppliers.

11. TSMC, Corporate Social Responsibility Report, 2019.

14. World Semiconductor Council, "Comments of the Associations of the World Semiconductor Council (WSC) on the Consultation Document on Proposed Amendments to the Prohibition of Certain Toxic Substances Regulations, 2012 for PFOS, PFOA, LC-PFCAs, HBCD, PBDEs, DP and DBDPE (December 2018)," February 2019. 15. Kelleher, "Intel's Challenge: Net-Zero GHGs Across Operations," 2022.

<sup>12.</sup> Intel, Corporate Responsibility Report, 2020 - 2021.

<sup>13.</sup> SEMI, Semiconductor Climate Consortium, 2022.

Table of Contents > Chapter 1: Infrastructure

# CONTEXT

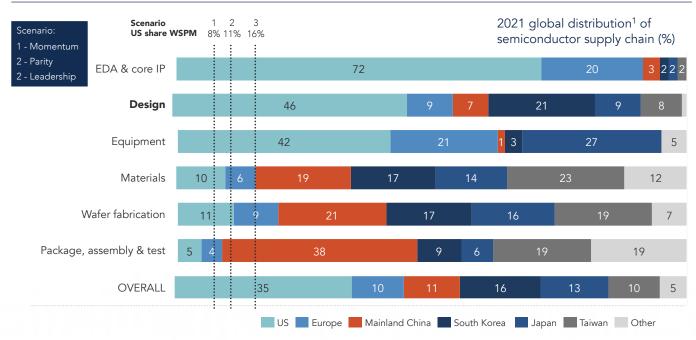

The semiconductor supply chain is extremely complex. Semiconductor production requires thousands of parts from around the world; however, individual steps in the supply chain tend to be regionally concentrated. The US is most at risk of supply chain disruption from materials, wafer fabrication, and PAT. In the Leadership Scenario, the US share of wafer fabrication doubles and supply of materials and PAT will likely need to be sourced from abroad. (See Exhibit 7).

#### Exhibit 7. The US Is Most Vulnerable in Materials, Fabs, and PAT

Source: Design estimate from "The Growing Challenge of Semiconductor Design Leadership" (Semiconductor Industry Association and BCG). All others from Capital IQ and BCG Analysis 1. For EDA and core IP, design, and manufacturing equipment, the regional breakdown is based on each company's revenues and headquarters location. For wafer fabrication and PAT, the regional breakdown is based on installed capacity and the geographic location of its facilities. For materials, the regional breakdown is based on the sales destination. Design revenues are based on fabless companies and the estimated share of IDM revenues attributable to design. Note: The revenues of integrated device manufacturers (IDMs) are disaggregated into estimates for design; wafer fabrication; and package, assembly, and test. WSPM = wafer starts per month, EDA = electronic design automation. Percentages may not add to 100 due to rounding.

16. US Geological Survey, 2022.

17. Australian Government Office of Chief Economist Outlook for Selected Critical Minerals, 2021.

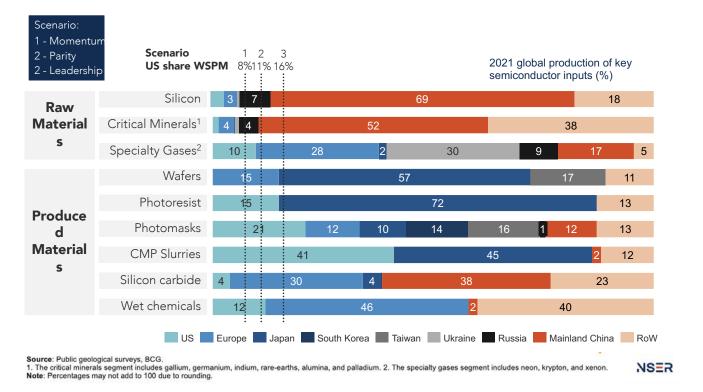

Mainland China, Russia, and Ukraine supply the majority of critical minerals, specialty gases, and silicon, all needed for semiconductor production. Notably, Mainland China produces 96% of gallium<sup>16</sup> and 85% of rare earth metals,<sup>17</sup> which are critical precursors for many modern compound semiconductors, and Russia and Ukraine house a high concentration of specialty gases, specifically neon and xenon.

#### Exhibit 8. The US Has a Weak Domestic Supply of Silicon and Critical Minerals

Recent increases in materials costs due to supply chain issues underscore the potential strain on materials supplies. For example, the price for phosphoric acid used in etching is up 100% in the last two years, the price of neon gas for lithography is up more than 100%, and the price of nickel for stainless steel is up 130%.<sup>18</sup> (See Exhibit 8).

Similarly, the US market share of capacity for wafer fabrication and PAT is low and has been declining. East Asia accounts for over 75% of global wafer fabrication capacity, while the US is home to less than 12% today.<sup>19</sup> And nearly 40% of all PAT occurs in mainland China, followed by Taiwan at 27%. In total, East Asia accounts for approximately 80% of all PAT capacity, with the US having less than 5% of global capacity.<sup>20</sup>

These points of concentration pose significant risks to the domestic supply of semiconductors resulting from natural or man-made disruptions in the flow of goods and services. A natural disaster or conflict affecting one of these regions or a single governing body with control of any point in the supply chain has the potential to disrupt the entire industry. If OEMs are unable to obtain even one semiconductor device within a bill of materials, cars cannot ship, new utilities infrastructure cannot be installed, and supply of defense systems cannot be assured.

18. Nikkei Asia, "From Chemicals to Gases, Chip Suppliers Reel as Materials Prices Surge," June 2022.

19. BCG/SIA, "Government Incentives and US Competitiveness in Semiconductor Manufacturing," Sept 2020.

20. BCG/SIA, "Strengthening the Global Semiconductor Value Chain in an Uncertain Era," April 2021.

As examples of past disruptions, in 2011, an earthquake and subsequent tsunami caused a nuclear power plant meltdown in Japan that affected 25% of the global production of silicon wafers and 75% of the hydrogen supply. In 2020, a one-hour power outage at a memory fab in Taiwan affected 10% of global dynamic randomaccess memory (DRAM) supply. And in early 2021, the combination of an ice storm in Texas and a fire at a fab in Japan added considerable pressure to an already constrained supply chain.<sup>21</sup>

To improve US supply resilience against future natural or man-made disruptions, the semiconductor supply chain must expand to encompass geographic and supplier diversity. The US should therefore actively promote the expansion of onshore, near-shore, and friendshore activities.

Many initiatives can encourage onshore expansion, including the use of existing and innovative technologies that reduce the intensity of labor along the supply chain, the aggregation of cross-industry demand, and the deployment of national incentives in line with competing markets. These efforts must be focused on areas of highest need, risk, and feasibility to make the largest sustainable impact on the supply chain. Trade policy is also a viable tool; however, it must be used carefully, or the US risks weakening its homegrown companies.

Markets in Eastern Europe, East Asia, and Africa have and will likely continue to have cost advantages for labor, land, and taxes compared to the US. In steps of the supply chain for which the US is at a comparative disadvantage or where natural resources are not abundant, the industry must expand its supply from friendly and nearshore nations.

As the industry responds to national selfsufficiency movements across the globe, the future of the semiconductor supply chain is uncertain. No matter how and where the supply chain evolves, however, the US must adopt new strategies to increase resilience.

21. BCG/SIA, "Strengthening the Global Semiconductor Value Chain in an Uncertain Era," April 2021.

To ensure US competitiveness in semiconductors, stakeholders must work together to increase supply chain resilience. Based on an extensive literature review and NSER participant input from industry, government, and academic leaders, three visions have been identified, along with supporting objectives and initiatives to drive this change.

#### VISION:

The US has dependable supply chains for the raw materials, consumables, intermediary products, and equipment needed by domestic manufacturing.

**Objective:** Expand dependable sources of raw materials, gases, consumables, and intermediary products from domestic and friendly sources.

$(\bigcirc)$

$\odot$

- **Initiative:** Identify shared materials used by other US industries (e.g., solar, batteries) to combine market power and improve supply.

- **Initiative:** Stockpile materials (e.g., gallium, silicon, rare metals) and gases (e.g., neon, helium, krypton) vulnerable to disruption in private and national defense stockpiles.

- **Initiative:** Innovate new manufacturing processes to utilize environmentally sustainable, recyclable, and readily available inputs.

- **Initiative:** Leverage CHIPS funding to expand domestic R&D and manufacturing of consumables and intermediary products.

**Objective:** Expand dependable domestic, nearshore, and friend-shore sources of manufacturing equipment.

- **Initiative:** Use CHIPS funding to expand the domestic manufacturing and assembly of equipment subsystems.

- Initiative: Use CHIPS funding for equipment R&D to design next- generation processes.

#### **VISION:**

The US reaches the Leadership Scenario for domestic manufacturing capacity of advanced and mature semiconductor devices.

Objective: Expand US wafer fabrication capabilities and increase capacity.

- **Initiative:** Quickly distribute CHIPS funding to expand and update manufacturing capacity for advanced semiconductors, for which the US has very little capacity today.

- **Initiative:** Quickly distribute CHIPS funding to expand manufacturing capacity for mature semiconductors, especially those required for critical infrastructure.

- Initiative: Plan projects that will manufacture the latest technologies of the future.

**Objective:** Increase domestic package, assembly, and test capacity and improve dependable access to offshored package, assembly, and test.

- **Initiative:** Leverage CHIPS funding to build domestic advanced PAT facilities and expand domestic traditional PAT to support critical infrastructure.

- Initiative: Leverage CHIPS funding to accelerate PAT manufacturing innovations.

- Initiative: Nearshore and friend-shore OSAT.

#### **VISION:**

The US maintains access to global markets and has global supply chain visibility to promote innovation and stability.

$(\bigcirc)$

**Objective:** Maintain the export of semiconductor goods and services not of concern to US security.

- **Initiative:** Work with policy makers to identify goods and services that are not of concern to US security.

- **Initiative:** Advocate for continued foreign market access for export of identified goods and services not of concern.

**Objective:** Maintain the free export of goods and services that are undifferentiated or for which there are viable substitutes.

- **Initiative:** Work with policymakers to identify goods and services with non-US origin substitutes.

- **Initiative:** Advocate for continued foreign market access for export of identified highly substitutable semiconductor goods and services.

**Objective:** Build a resilient global supply chain that is transparent and digitized for optimization modeling.

- **Initiative:** Create or identify a program to standardize, collect, and analyze crossindustry data.

- **Initiative:** Aggregate data on end-to-end supply chain trade flows for inputs and outputs at the most granular level.

- **Initiative:** Create real-time data analytics platforms to model and understand key constraints and disruptions from supply, manufacturing, transportation, and logistics perspectives.

# **Chapter 3: Workforce**

# CONTEXT

Some 277,000 people are directly employed by the US semiconductor design and manufacturing industry.<sup>22</sup> Roles include engineers and scientists; technicians, operators, and machinists; and businesspeople and managers. Another 670,000 people are indirectly employed by the industry,<sup>23</sup> with roles in construction, materials handling, and equipment manufacturing and installation.

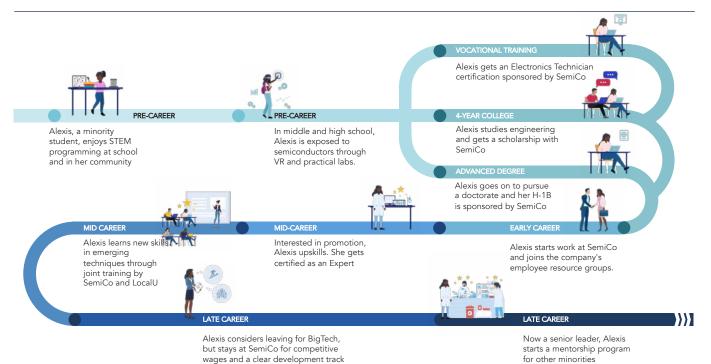

The paths to entering the semiconductor industry are countless. Training may be delivered on the job or through formal programs and institutions that give certifications, degrees, and even PhDs in just about every subject area, from liberal arts to nanoscale engineering.( See Exhibit 9).

#### Exhibit 9. The Semiconductor Talent Pipeline is Long and Complex

Source: BCG, NSER.

The importance of these workers cannot be overstated, and the gap between the industry's talent needs and its available skilled resources is growing, both for those directly employed by the industry and those indirectly employed. Critical changes in government policy, along with greater collaboration among states, industry leaders, and educators, are needed to immediately increase the skilled labor available in the semiconductor talent pool.

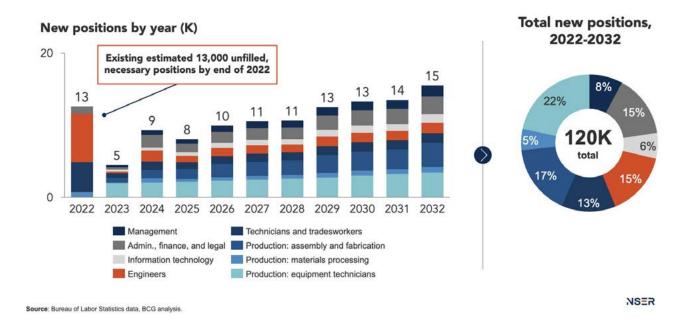

To begin, future domestic semiconductor manufacturing will require growing the labor force from 190,000 employees in 2022 to 310,000 by 2032 to support the Leadership Scenario. This is a tall order as the semiconductor manufacturing industry is already understaffed by an estimated 13,000 workers with the largest gaps in engineering (7,000) and technicians and trades workers (4,000). Of the 120,000 estimated positions to be filled in the next 10 years, the areas of greatest need will be equipment technicians (26,000), assemblers and fabricators (20,000), and engineers (18,000) reflecting an expansion of manufacturing production relative to management. (See Exhibit 10).

NSER

23. Semiconductor Industry Association, "State of the Industry," 2021

<sup>22.</sup> Semiconductor Industry Association and Oxford Economics, "Chipping In: The U.S. Semiconductor Industry Workforce and How Federal Incentives Will Increase Domestic Jobs," 2021.

# Exhibit 10. Managing and operating fabs under the Leadership Scenario will create over 120,000 new positions

In addition, based on extrapolating design workforce requirements from a BCG and SIA

report an additional 3 years, the US design industry will demand 100,000 workers by 2033. However, current inflow rates will result in only 67,000 workers, leaving a deficit of 32,000.<sup>24</sup>

Future manufacturing expansion will also generate demand for 850,000 workers across other industries through indirect and induced job creation. The indirect, or supply-chain, effect encompasses upstream jobs that support production of the final product, while the induced effect, in turn, reflects downstream job creation resulting from the industry's labor income, profits, and household consumption.

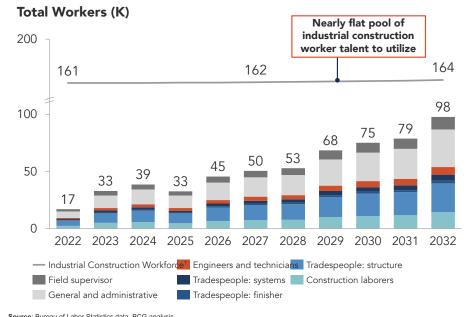

One particularly urgent area of indirect job creation is in construction. Each fab requires approximately 5,000 on-site workers for up to three years to complete, depending on fab size and construction circumstances. Based on capital investments in fab construction from NSER Leadership Scenario, the US will require 100,000 construction workers for fab construction by 2032, compared to about 17,000 working on semiconductor industry construction in 2022. The semiconductor industry can draw from a large industrial workforce of over 150,000, but it must compete with other industries, such as pharmaceuticals and chemicals, which are expected to see increased demand as well. (See Exhibit 11).

24. BCG/SIA, "The Growing Challenge of Semiconductor Design Leadership," November 2022.

#### Exhibit 11. Fab Construction Requires 100,000 Workers in 2032 for the Leadership Scenario

Source: Bureau of Labor Statistics data, BCG analysis. 1. The industrial construction workforce represents the pool of available construction workforce from which fab construction workers will be needed 2. Tradespeople job types: systems—HVAC, electrical, plumbing; finishing—painters, paperhangers, plasterers; structure—carpenters, masons, roofers.

Meeting these workforce needs means facing many challenges. First, there is declining interest in and proficiency with STEM subjects among youth in the United States. Data from the Institution of Engineering and Technology shows that, since 2015, interest from 9- to 12-year-old children in science has fallen by 10%; in design by 12%; and in information, computing, and technology by 14%.<sup>25</sup> In addition, where 15-yearold children in other countries show increased proficiency in math and sciences, the US average has remained largely stagnant.<sup>26</sup>

Second, employment at a semiconductor company is frequently not a skilled worker's first choice. For those who do take employment in STEM, the preference is for computer science occupations at companies such as Meta, Apple, Amazon, Netflix, or Google, and 50% of all STEM graduates pursue computer sciences.<sup>27</sup>

Third, the US relies heavily on foreign-born talent, but immigration pathways are not growing with industry demand. Since 2015, the number of visaholding foreign-born graduates has increased 15% more than that of US-born graduates, continuing a decades-long trend toward increased reliance on global talent.<sup>28</sup> However, the total cap on the number of foreign-born advanced-degree holders who can receive an H-1B employment-based nonimmigrant visa has not changed since 2004, and the employment-based green card cap has remained unchanged at 140,000 per year since 1990.<sup>29</sup>

26. Organisation for Economic Co-operation and Development, Programme for International Student Assessment, 2018.

27. U.S. Census Bureau, "Does Majoring in STEM Lead to a STEM Job After Graduation?" 2021.

28. National Center for Science and Engineering Statistics, "Survey of Earned Doctorates by Citizenship and Field of Study," 2020.

29. American Immigration Council, H-1B Visa Program, 2021.

#### Construction Workforce by Position (2032)

#### 44K G&A and field supervisors

- General & Administrative: Overhead workforce that facilitates administrative and management responsibilities

- Field supervisors: On-site staff that ensure construction designs and plans are followed and executed smoothly.

#### 47K Tradespeople and laborers<sup>2</sup>

Skilled workers specialized in a particular construction trade (structure, finishing, systems), and unskilled laborers

**7K Engineers and technicians** Professionals responsible for designing, facilitating, and executing construction

engineering plans

In response, several former national security officials wrote to Congress asking that immigrants with advanced STEM degrees not face green card limits, to make the country more competitive. Their letter stated: "In today's technology competition, the most powerful and enduring asymmetric advantage America has is its ability to attract and retain the world's best and brightest." That advantage is deteriorating. Yet losing comparative advantage in the semiconductor industry is a national economic and security risk.

As the US turns talent away, other regions have more opportunities for them. For example, South Korea produces less than half the graduates it needs each year to maintain its semiconductor workforce.<sup>30</sup> Even mainland China's 1.4 billion citizens aren't producing enough skilled talent; the region's Semiconductor Industry Association estimated a 300,000 laborer deficit in 2019. The US can expect the global competition for talent to only intensify in coming years.

Finally, the industry does not attract a fully diverse set of candidates, artificially limiting its own pool of talent. Though the semiconductor industry has a greater share (48%) of non-White workers compared to other manufacturing sectors, only 4% of the workforce identifies as Black and 13% as Hispanic,<sup>31</sup> despite constituting 14% and 19% of the general population in the US, respectively.<sup>32</sup> In addition, the most widely available information indicates that the workforce is heavily male-dominated. Less than 25% of the workforce is female versus 50% US-wide, and most semiconductor companies report that just 10% of their director-and-above roles are filled by females.<sup>33</sup>

Each of these issues makes closing the skilled-talent shortage difficult and complex. Immediate and ongoing action in terms of education and immigration policy, along with a collaborative approach among all stakeholders, is critical to increasing the pool of skilled labor and enhancing US leadership across the value chain.

30. Korea Semiconductor Industry Association, 2019.

- 31. Semiconductor Industry Association and Oxford Economics, "Chipping In: The U.S. Semiconductor Industry Workforce and How Federal Incentives will Increase Domestic Jobs," May 2021.

- 32. United Stat+, Population estimates by race, 2020.

- 33. Women in the semiconductor industry, 2019, Global Semiconductor Alliance

To ensure US competitiveness in the semiconductor industry, policy makers, academia, and the industry must work together to reduce and ultimately eliminate the workforce shortage. Based on an extensive literature review and NSER participant input from industry, government, and academic leaders, NSER has identified three visions and supporting objectives and initiatives to drive this change.

$\bigcirc$

#### **VISION:**

The number of students who enter the semiconductor pipeline increases significantly due to teaching, mentoring, and transitioning a diverse population into the industry.

**Objective:** Foster pre-career (school-age through high school) interest in STEM careers in general and semiconductor work in particular.

• **Initiative:** Expose pre-career students to semiconductor work during school-based activities by increasing the engagement among semiconductor companies, students, teachers, and administrators.

**Example:** Samsung Austin Semiconductor hosts STEM Academies for middle and high school students that explains the manufacturing process, demonstrates how to put on a smock, and includes a career panel.

• **Initiative:** Embed accessible STEM content into play activities at camps, libraries, and parks, rec centers, and other areas, to reach students where they are.

**Example:** STEMLibraries offers toolkits to create and promote STEM learning centers in libraries, the Institute of Electrical and Electronics Engineers raises funds for libraries to develop science kits for children to check-out similar to books,<sup>4</sup> and the Institute of Museum and Library Services offers grants to fund a variety of library and museum initiatives.<sup>35</sup>

**Example:** The Texas Workforce Commission awarded \$1.26 million to universities and community colleges, which allowed 1,351 students age 14 to 21 to attend STEM camps;<sup>36</sup> Science Camps of America also provides scholarships.<sup>37</sup>

**Example:** Grants through the U.S. Department of Education's 21st Century Community Learning Centers offer STEM programming in national parks.<sup>38</sup>

• **Initiative:** Drive parent and youth awareness of semiconductor work as a career of choice by developing fun and accessible programming.

**Example:** Partner with learning programs such as PBS or Science Channel's series "*How It's Made*," or with prominent STEM influencers such as Neil deGrasse Tyson, Destin Sandlin, Mark Rober, or Hank Greene, to create updated semiconductor content highlighting different types of workers across the industry.<sup>39</sup>

**Example:** The University of Arizona's Wyant College of Optical Sciences hosts "Laser Fun Day," both in person and virtually, aimed at teaching the public about the optical sciences and shedding light on the opportunity that studying the optical sciences can provide students.<sup>40</sup>

- 34. STEMlibraries.org. and Institute of Electrical and Electronics Engineers, Science Kits for Public Libraries.

- 35. Institute of Museum and Library Services, Grant Programs.

- 36. Texas Workforce Commission (TWC), "TWC Awards Grants for 1351 Students to Attend High-Tech Summer Camps," May 2017.

- 37. Science Camps of America, Scholarship Fund.

- 38. National Environmental Education Foundation (NEEF), "NEEF Announces 2022-2023 Awardees of NPS-21st Century Community Learning Centers (CCLC) Greening STEM Grant," July 2022.

- 39. Science Channel, *How It's Made*, Season 9, Episode 5.

- 40. Laser Fund Day, https://laserfunday.org/, October 2022.

• **Initiative:** Demonstrate the positive impact of semiconductor careers by supporting accessible civic activities in semiconductor training and manufacturing hubs.

**Example:** The NXP Americas Community Impact program offers grants to support education, health and wellness, and the environment in the communities where it operates.<sup>41</sup>

**Example:** onsemi's Giving Now program issues science, technology, engineering, arts, and mathematics education grants to eligible organizations in the communities where they operate.<sup>42</sup>

**Objective:** Increase primary and secondary student proficiency with STEM so that the US keeps pace with or exceeds other countries' scores on the Program for International Student Assessment.<sup>43</sup>

• **Initiative:** Develop a semiconductor-specific training curriculum and host it on publicly available platforms for educators and students to access, such as Khan Academy, Coursera, or LinkedIn Learning.

**Example:** Available grants include those from the William + Flora Hewlett Foundation,<sup>44</sup> the US Department of Education Open Textbooks Pilot Program,<sup>45</sup> and the National Science Foundation's Pathways to Enable Open-Source Ecosystems (POSE).<sup>46</sup>

• **Initiative:** Increase the number of STEM-designated middle and high schools (merit-based or openenrollment) in every state and include semiconductor-related courses.

**Example:** The Illinois Mathematics and Science Academy<sup>47</sup> and the Texas Science, Technology, Engineering, and Mathematics Initiative (T-STEM) are both STEM-designated.<sup>48</sup>

• **Initiative:** Increase educator comfort with STEM concepts by providing initial and professional development in STEM concepts.

**Example:** The National Teacher Training Institute<sup>49</sup> and SIA partnership, the National Science Teachers Association,<sup>50</sup> the American Society for Engineering Education,<sup>51</sup> and Texas A&M Engineering Experiment Station (TEES) all offer STEM training for educators.<sup>52</sup>

**Example:** The Supporting Effective Educator Development (SEED) Grant provides \$65 million in funding to develop and enhance the skills of educators. (See footnotes for additional US Department of Education grants.)<sup>53</sup>

**Objective:** Increase the number of graduates from career training programs (on-the-job, vocational, technical, two-year, four-year, and advanced degrees) who pursue work in the semiconductor industry.

• **Initiative:** Develop wraparound support for under-resourced students that enable attendance and success in training programs.

**Example:** Samsung Austin Semiconductor provides scholarships for under-represented students to pay for books, rent, etc. participating in a CPT program through Austin Community College.

- **Initiative:** Measure the effectiveness of training programs by collecting data, such as entrance and exit interviews, career services records, cost to attend, graduation rates, hire rates, and industry retention rates, and compare program feasibility with impact.

- 41. NXP, Americas Community Impact.

- 43. National Science Foundation, How Do U.S. 15-Year-Olds Compare with Students From Other Countries in Math and Science?, 2012.

- 44. Hewlett Foundation, Open Education.

- 45. U.S. Department of Education, Open Textbooks Pilot Program.

- 46. National Science Foundation, Pathways to Enable Open-Source Ecosystems.

- 47. Illinois Mathematics and Science Academy.

- 48. Texas Education Agency.

- 49. Phoenix Business Journals, "Semiconductor Industry to Co-host Teacher Training Seminar," November 2000.

- 50. National Science Teaching Association.

- American Society for Engineering Education.

Texas A&M University, Workforce Development.

- 53. U.S. Department of Education.

<sup>42.</sup> onsemi, Giving Now Program.

• Initiative: Conduct a survey of students to understand which barriers are currently the most likely to prevent them from pursuing a semiconductor career, and create comprehensive strategies to overcome those barriers.<sup>54</sup>

**Example:** There are over 30 grants available for FY 2022 through the Educational Credit Management Corporation (ECMC) Foundation, which improves higher education and career success among underserved populations.<sup>55</sup>

**Example:** NC State University offers funding opportunities for international, underrepresented, minority, and disabled students in STEM.<sup>56</sup>

• Initiative: Adapt prerequisite curriculums to be context-based, and offer flexible training programs.

**Example:** The healthcare and other industries offer training programs with pre-requisites adapted to the career context.<sup>57</sup>

**Example:** Modular, hybrid, online, and part-time evening and weekend options maximize participation and accessibility and allow students to earn while learning.

• Initiative: Increase the nation's training capacity at all levels.

**Example:** Intel partnered with Maricopa Community Colleges to establish a new semiconductor manufacturing program that prepares technicians through hands-on learning in an accelerated two-week program.<sup>58</sup>

• **Initiative:** Create accelerated tracks for workers from adjacent industries with skillsets that could be adapted to the semiconductor industry.

**Example:** The healthcare industry offers courses of study, such as Clark State College's Paramedic to RN Transition program.<sup>59</sup>

**Example:** New York recently announced the Veteran Semiconductor Training and Experience Program (VET S.T.E.P) as an official career skills program, part of the Department of Defense SkillBridge network. SkillBridge programs help service members from all branches transition into civilian careers through training, internships, and other work experience.

• **Initiative:** Increase the availability and utilization of practical learning experiences by creating internship, externship, and apprenticeship opportunities at every semiconductor company.

**Example:** The Massachusetts Learn to Earn Initiative provides individuals receiving public assistance with the support, skills, and credentials they need to gain and retain employment in high-demand occupations.<sup>60</sup>

**Example:** The competency-based SEMI Industry Approved Apprenticeship Program (IAAP) identifies skill gaps and helps companies offer targeted training to workers pursuing careers in electronics.<sup>61</sup>

- **Initiative:** Partner with regional R&D universities to attract faculty and top researchers in order to accelerate workforce readiness and drive innovation and breakthrough discoveries.

- 54 .Newsroom US Cellular, "US cellular Survey: Nearly Half of Students See Lack of Diversity, Cost as a Barrier to Pursuing STEM Careers," March 2022. 55. ECMC Foundation.

- 56. North Carolina State University, Funding Opportunities for International, Underrepresented Minority and Disabled Students in STEM.

- 57. David Armstrong & Judith C. Poe, "The Science of Human Health—A Context-Based Chemistry Course for Non-Science Majors Incorporating Systems Thinking," September 2020.

- 58. Businesswire, "Maricopa Community Colleges and Intel to Launch New Semiconductor Manufacturing Workforce Development Initiative," March 2022.

- 59. Clark State College, Registered Nursing Paramedic to RN Transition

- 60. Commonwealth of Massachusetts, Learn to Earn initiative.

61. SEMI, "SEMI Partners with Global Foundries to Offer Apprenticeship Program Aimed at Building the Electronics Talent Pipeline, August 2020.

**Example:** Intel is investing \$100 million over the next decade to establish semiconductor manufacturing education and research collaborations with universities, community colleges, and technical educators across the US.<sup>62</sup>

**Objective:** Improve the process for highly needed talent to immigrate to the US and transition into the workforce.

- **Initiative:** Lobby to change the immigrant and nonimmigrant visa process so that candidates receive a preliminary approval rapidly and can work while waiting for final approval.

- **Initiative:** Encourage in-house and industry association lobbyists to push for exemptions on caps to H-1B, H-2 (temporary), H-3 (trainee) and Employment Based (EB) visas for semiconductor workers.

**Example:** SIA petitioned the US Department of Homeland Security to prioritize advanced degree holders in the H-1B lottery and to eliminate preregistration requirements.<sup>63</sup> Similarly, industry leaders petitioned for immigration law restructuring immediately after the passage of the CHIPS Act.<sup>64</sup>

• **Initiative:** Assist workers in navigating the visa process, through contracted legal support or in-house resources, to increase the attractiveness of semiconductor work.

**Example:** The Dartmouth College Office of Visa and Immigration Services (OVIS) offers of comprehensive assistance to international students, scholars, faculty, and staff on campus.<sup>65</sup>

$\bigcirc$

• **Initiative:** Perform outreach campaigns in multiple languages and through multiple mediums (e.g., TV, neighborhood walks, radio) to reach the full US population.

#### **VISION:**

The semiconductor industry retains its talent pool by reversing addressable attrition factors.

**Objective:** Continue the comprehensive belonging, diversity, equity, and inclusion efforts that recruited workers to the industry in order to establish comprehensive retention strategies that increase workplace satisfaction.

• **Initiative:** Conduct company and industry assessments that collect and measure key diversity, equity, and inclusion satisfaction factors.

**Example:** The SEMI Foundation Diversity, Equity, and Inclusion Roadmap aims to help the organization's members transform the way they hire and retain employees and build a more diverse workforce.<sup>66</sup>

• Initiative: Develop a comprehensive and strategic program that addresses key DE&I satisfaction factors.

**Example:** The International Society for Optics and Photonics developed a toolkit that companies can use to instill actionable equity, diversity, and inclusion best practices into their company culture.<sup>67</sup>

**Example:** The industry-wide Women in Semiconductors (WIS) conference focuses on creating a culture of mentorship, sponsorship, and support that enables women to succeed in the semiconductor industry.<sup>68</sup>

62. Intel Newsroom, "Intel Invests \$100M in Ohio and National Semiconductor Education and Research," March 2022.

63. SIA, "Registration Requirement for Petitioners Seeking to File H-1B Petitions on Behalf of Cap-Subject Aliens (DHS Docket Number-USCIS-2008-0014) (RIN 1615-AB71)," January 2019.

- 65. Dartmouth College, Office of Visa and Immigration Services.

- 66. SEMI, "Diversity, Equity and Inclusion Roadmap," 2021.

- 67. SPIE, "Equity, Diversity, and Inclusion: A New Strategies Framework from SPIE," January 2021.

- 68. SEMI, "Women in Semiconductors—WIS 2022," May 2022.

<sup>64.</sup> The Hill, "Semiconductor Giants Call for Immigration Law Restructuring," August 2022.

• **Initiative:** Measure the effectiveness of strategic industry diversity initiatives, and publish annually to drive current and potential employees' awareness of industry DE&I efforts.

**Example:** NXP Semiconductors<sup>69</sup> and Micron's websites<sup>70</sup> both document their progress in improving representation, pay equity, inclusion, advocacy, social justice, and financial and supplier diversity.

• **Initiative:** Increase the number of semiconductor companies participating in programs that are deliberately attempting to increase gender or racial parity in the workplace.

**Example:** Global Semiconductor Alliance's CEO has publically pledged to intentionally recruit, retain, develop, and advance women.<sup>71</sup>

**Objective:** Increase employee satisfaction with their career impact by providing them with examples of how their work is directly applied and how it contributes to the overall economy.

- **Initiative:** Provide opportunities for skilled workers to see the practical applications of their work through hands-on experiences.

- **Initiative:** Encourage industry publications to illustrate major advances and discoveries and crosspublish in other respected journals.

**Example:** A SEMI survey found that 60% of executives considered the prestige of semiconductor careers low in comparison with other high-tech careers.<sup>72</sup>

• **Initiative:** Develop social impact rotations at both company and national levels by sponsoring student mentorships, teaching rotations, exchanges in developing countries, and other opportunities to contribute to social good.

**Example:** The Intel RISE program provides employees with opportunities to use their professional skills to benefit their community.<sup>73</sup>

**Objective:** Make compensation transparent within companies, and make industry averages competitive with similar industries and countries.

• **Initiative:** Develop pay bands tied to skill levels for workers such as operators, technicians, engineers, and scientists that are roughly equivalent from semiconductor company to semiconductor company.

**Example:** Companies such as Amazon and Google use leveling for their employees that skilled workers can employ to evaluate the competitiveness of job offers. Although hardware and mechanical engineers are included in salary comparison sites like levels.fyi,<sup>74</sup> many other skilled positions are not.

• **Initiative:** Benchmark compensation in similar industries and for equivalent training both in the US and internationally.

**Example:** The International Society of Optics and Photonics conducts an annual global survey of engineers and scientists in both industry and academia.<sup>75</sup>

• **Initiative:** Adjust compensation to compete with other countries and similar industries using innovative compensation packages.

**Example:** In addition to direct compensation, permanent citizenship assistance, pay for certification, tuition reimbursement for advanced degrees, and healthcare and family leave benefits are all factors in compensation satisfaction.

69. NXP, Diversity and Inclusion.

- 70. Micron Technology, Inc.

- 71. Global Semiconductor Alliance, CEO Pledge.

- 2017 SEMI-Deloitte Workforce Study.

73. Intel, Intel Involved Skills-based Volunteering, 2010.

- 74. Levels.fyi, Open Compensation Data.

- 75. SPIE, Global Salary Report Hub.

**Objective:** Create developmental and promotion path journeys so that workers see a clear way forward to obtaining higher pay, skills, and responsibilities.

- **Initiative:** Establish standard career ladders and lattices that are transferable and equivalent across a company's different offices and geographic locations.

- **Initiative:** Establish leadership development programs or standard promotion paths and ensure that leadership represents the demographics of the entire company.

**Example:** Global Semiconductor Alliance's Women's Leadership Initiative (WLI) not only recruits females to the industry but seeks to back female-owned startups and create "inspiration and sponsorship for the next generation of female leaders."<sup>76</sup>

(D)

#### **VISION:**

The workforce is adaptable to the advancing needs of the industry.

Objective: Reskill workers whose skills no longer meet industry needs due to technology advancements.

- **Initiative:** Survey industry and academia to understand what skills are currently being taught, which are most in demand, and where the greatest gaps lie.

- **Initiative:** Create a skill taxonomy that maps skills to roles, establish standard certifications, and implement these across the industry by including them in job advertisements and course descriptions.

**Example:** The project management professional (PMP) certification is a well-recognized and transferrable credential.<sup>77</sup>

• **Initiative:** Provide retraining for skills through lattice programs within companies and refresher courses in academia. Leverage platforms that offer free semiconductor-specific training opportunities and immersive AR/VR training where possible.

Example: SEMITRACKS offers a variety of public courses.78

**Example:** Nanyang Technological University offers training of semiconductor machines based on virtual reality (VR) course<sup>79</sup> and Siemens offers Virtual Reality and Field Operator Training.<sup>80</sup>

#### Objective: Upskill workers with an interest in and aptitude for advanced training.

• Initiative: Develop advanced training programs and include an "expert"- designation on skill certificates.

**Example:** The Department of Defense and Massachusetts Institute of Technology (MIT) have teamed up to offer an Open edX platform for advanced manufacturing technologies education.<sup>81</sup>